By TUNG Chen-Yuan, PhD, Taiwan’s Representative to Singapore

In the global race for technological supremacy, semiconductors remain the most strategically consequential industry. In recent years, China has repeatedly claimed breakthroughs in chip self-sufficiency, from 7-nanometer to so-called 5-nanometer-class processes, drawing widespread international attention. Yet a closer look at the underlying technology and industrial structure suggests that whether China can truly catch up with global leaders in advanced manufacturing is far more complex than headlines imply.

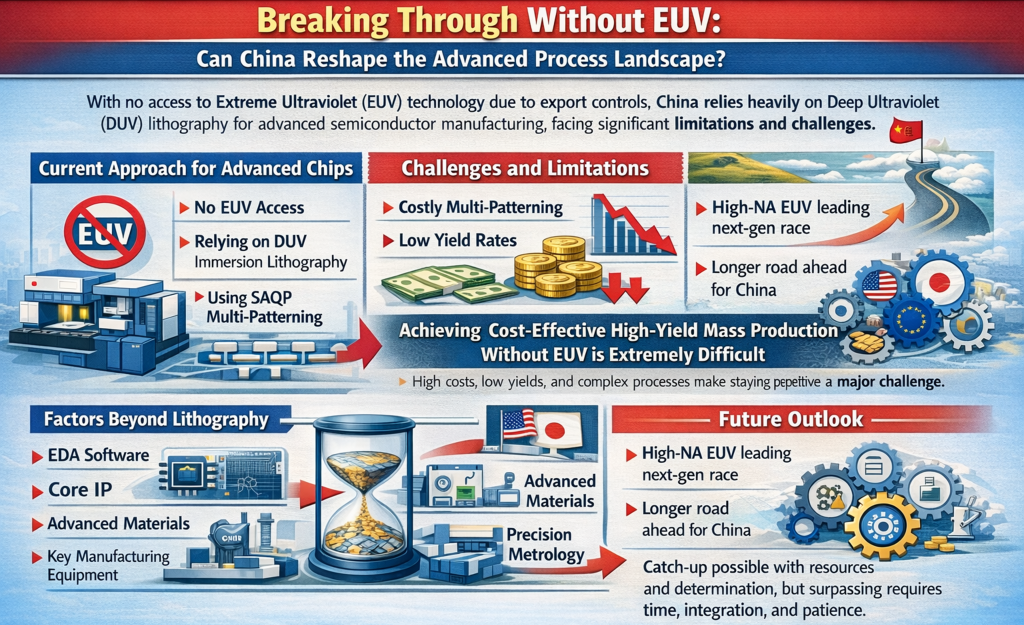

The critical threshold today lies in extreme ultraviolet (EUV) lithography. For 3-nanometer nodes and below, EUV is virtually indispensable. However, due to export controls, SMIC—China’s leading foundry—cannot access EUV systems and must rely instead on deep ultraviolet (DUV) immersion lithography. To push beyond physical limits, it has adopted multi-patterning techniques such as self-aligned quadruple patterning (SAQP), increasing process steps to achieve finer line widths. This strategy—using engineering intensity to compensate for equipment constraints—has produced tangible progress, and many observers believe SMIC can now fabricate near–7-nanometer chips using DUV.

According to TechInsights’ teardown analysis, Huawei’s Kirin 9030 and 9030 Pro chips, used in the Mate 80 series, are manufactured with SMIC’s N+3 process. Technically, however, N+3 represents an extension of its existing 7-nanometer (N+2) platform rather than a genuine leap into the 5-nanometer generation. The front-end transistor architecture shows no fundamental shift; improvements in performance and density stem largely from tighter back-end metal pitch and close design–process co-optimization. In essence, this is an exercise in extreme refinement within a DUV framework, not a generational transition built on EUV. Its technological ceiling is therefore increasingly visible.

More formidable challenges lie in cost and yield. Multi-patterning entails more steps, higher overlay error risks, and longer production cycles. Each additional exposure increases the probability of defects and variability. External estimates suggest SMIC’s 7-nanometer yield hovers around 50 percent; pushing toward a 5-nanometer-class node could see yields fall to 30–40 percent, with production costs 40–50 percent higher than TSMC’s comparable processes. While precise figures remain debated, the structural reality is clear: without EUV, achieving high yield, competitive cost, and stable mass production simultaneously is extraordinarily difficult.

Even access to EUV would not guarantee smooth progress. Intel and Samsung both operate EUV lines yet have faced yield bottlenecks and cost pressures at advanced nodes. This underscores a key point: advanced manufacturing is not solved simply by purchasing equipment. TSMC’s advantage lies not only in its machines, but in decades of accumulated process integration expertise, defect management, supply-chain coordination, and disciplined high-volume manufacturing. Advanced fabrication is fundamentally a systems endeavor—equipment is merely the entry ticket; execution and integration determine the outcome.

Lithography itself is only one element of a broader ecosystem. Cutting-edge production depends on EDA software, core IP architectures, advanced materials, precision metrology, and critical deposition and etching tools—fields still dominated by U.S., European, and Japanese firms. These segments are tightly interwoven, forming a highly coordinated technological network. A breakthrough in one area does not automatically resolve bottlenecks elsewhere. The real challenge is not a single-point advance, but the reconstruction of an entire ecosystem.

Chinese firms have not stood still. Huawei and Shanghai Micro Electronics Equipment (SMEE) have filed patents related to EUV, signaling long-term ambitions for technological autonomy. Yet the journey from patent concepts to stable mass production often spans decades of accumulated expertise and global supply-chain integration. ASML’s successful commercialization of EUV itself reflects sustained multinational collaboration and long-term R&D investment. Replicating such a model under relatively constrained conditions would be an immense undertaking.

Meanwhile, the technological frontier continues to advance. In early 2025, Intel began deploying High-NA EUV in production, marking the next phase of competition beyond 3 nanometers. Even if China were to develop Low-NA EUV systems in the future, it would still confront an ever-moving benchmark. Semiconductor competition is not a static gap to be closed, but a constantly shifting race.

Overall, China’s semiconductor sector has demonstrated notable resilience and engineering capability, advancing despite significant constraints. Yet the absence of EUV, reliance on DUV multi-patterning, dependence on foreign EDA and core IP, and persistent cost and yield pressures constitute structural challenges. True leadership in semiconductors is not defined by possession of a single critical tool, but by mastery of an integrated industrial ecosystem. Catching up may be fueled by determination and resources; surpassing others, however, requires time, institutional depth, and systemic accumulation—variables that rarely compress on command.

📥 《Taiwan at the Core: Strategic Partner in Global Semiconductor Landscape and Realignment》Simplified E-Book Edition (Edited by the Taipei Representative Office in Singapore, available for free download):

https://maintain.taiwanembassy.org/sg_en/wp-content/uploads/sites/86/2026/01/29012026_Final5.pdf

📚 《Taiwan at the Core: Strategic Partner in Global Semiconductor Landscape and Realignment》Order the Print Edition from the Publisher:

About the Author:

Dr. Tung Chen-Yuan is currently Taiwan’s Representative to Singapore. He was Minister of the Overseas Community Affairs Council of the Republic of China (Taiwan) from June 2020 till January 2023. He was Taiwan’s ambassador to Thailand from July 2017 until May 2020, senior advisor at the National Security Council from October 2016 until July 2017, and Spokesman of the Executive Yuan from May to September 2016. Before taking office, Dr. Tung was a distinguished professor at the Graduate Institute of Development Studies, National Chengchi University (Taiwan). He received his Ph.D. degree in international affairs from the School of Advanced International Studies (SAIS), Johns Hopkins University. From September 2006 to May 2008, he was vice chairman of the Mainland Affairs Council, Executive Yuan. His areas of expertise include international political economy, China’s economic development, and prediction markets.